从Bring-up到Shift-left Siemens EDA以一致性工具链串起完善先进验证流程

AI 时代的系统级芯片规模持续放大,软硬件整合也更复杂,验证团队不仅要持续追求效率,更要在设计早期就能以接近真实系统的方式观察行为,建立稳定、可复制的流程,来降低风险并推进专案时程。

为此,Siemens EDA于1月中旬举办「先进验证技术日」,从硬件加速、FPGA原型到前期建模分析等路径,说明如何以一致性工具链串起完整的端对端验证流程,并透过客户导入案例经验分享与合作夥伴生态系资源介绍,让与会者了解其中效益与优势。

打击关键痛点:Veloce proFPGA CS加速bring-up、设计分割与除错

Siemens EDA资深产品经理Romain Petit首先概述新一代FPGA原型验证技术的进展。他形容,要将复杂ASIC设计成功在原型平台上运作,「是一件真的很让人头痛、也最容易拖慢专案节奏的事;」而加速系统启动(bring-up)的关键,在于平台必须可扩展且能弹性部署。

以 AMD Versal Premium VP1902 自适应SoC为核心的模块化设计Veloce proFPGA CS平台,涵盖适合日常操作的单FPGA桌上型电脑,到服务器/数据中心等级的多FPGA、数十亿逻辑闸系统,并支持线上管理与多专案共享,能依设计规模配置资源。

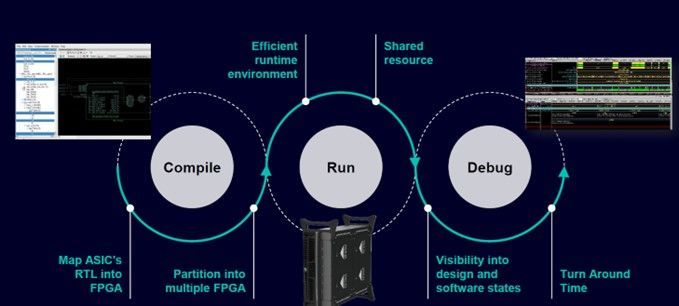

另一个重要的bring-up加速手段,是透过软件将大量手动工程转为可重现、可自动化的流程。Petit指出,由于ASIC与FPGA架构不可能一对一映射,加上时序收敛需要反覆迭代,界面协定整合与除错高度复杂,若仰赖人工操作容易导致错误与结果不一致;VPS (Veloce Prototyping implementation Software)以「编译-执行-除错」(Compile–Run–Debug)三阶段工作流程,将映射RTL至FPGA、多FPGA设计分割,以及高效率Runtime环境与共享资源、设计与软件状态的可视性等功能串联起来,形成一致、可重复并持续最佳化的流水线,进而缩短周转时间。

VPS的另一个核心功能是将多FPGA的设计分割与连线、时脉树建置(包含闸控时脉转换与时脉分配),以及存储器处理(自动存储器推断、外部存储器整合与软件模型)等任务纳入自动化,让系统更快进入可运作状态,再循序把效能推向最佳化。Petit强调,VPS透过支持批次(batch)与图形化界面(GUI),协助使用者监控编译流程与品质,并以设计注记、时脉树与网表浏览、时序分析及分割检视等机制提升除错效率。

多FPGA原型验证渐成常态,设计分割是专案能否落地、除错能否有效推进的关键。Siemens EDA应用工程顾问David Lu指出,单一FPGA往往装不下整体系统,若设计维持单体(monolithic)结构,实作与除错难度会大增、资源管理也不易。透过合理分割可降低复杂度、改善时序与绕线可达性,并提升扩充与维护弹性。他补充,VPS支持在「全手动到全自动」间弹性取舍的分割策略:可人工主导切分与连线,或以自动化工具切分并建议互连以追求效能,也可先手动设定粗粒度约束再交由工具最佳化,兼顾bring-up速度与效能。

在除错方面,David Lu表示VPS以串流化(streaming)架构为核心,支持多种触发方式并可输出波形供分析,在维持原型速度下提升可观测性,缩短问题定位与除错周期;搭配完整可视性与分组波形分析,使原型平台的除错生产力更接近硬件模拟。同时透过结构化分割与自动分割的可预期品质与资源最佳化,再辅以手动调校提升效能与时序裕度,可在多FPGA架构下兼顾可靠度与长期扩展性。

来自 IC 设计业者凌阳(Sunplus)的代表也分享大型设计导入 proFPGA CS的实务经验,聚焦原型验证在除错、波形观测与环境建置上的常见痛点,对自动分割带来的效率提升与工程便利性给予正向回馈。

从一致性到左移:System VIP、Innexis与车用开发实例

在原型bring-up与除错之外,另一个挑战是让不同阶段的验证结果对齐,避免流程碎片化。Siemens EDA的系统级验证IP (Avery VIP)研发经理Ken Huang指出,VIP的价值不只在经验证的通讯协定IP,而是以「一致性核心」(unified kernel)维持跨阶段对应关系(correlation),让测试意图与观测结果能延伸到不同平台,提升一致性与效率。

另一方面,软件架构师Marco Liu则强调「左移」(shift-left)的重要性。Siemens EDA的Innexis矽前(pre-silicon)虚拟平台,透过整合DevPro开发/除错环境与ANA (Architecture Native Acceleration)原生加速,将高效能建模与分析移到RTL之前,使操作系统/应用程序与系统行为能更早运作、更快发现瓶颈,将验证由后段补救转为前段预防。

以车用SoC开发情境为实例,Siemens EDA资深客户技术经理Charles Kuo指出,软件定义车辆(SDV)促使车厂必须提升运算效能、缩短设计周期并支持长期OTA,然车辆硬件不但开发时程长、昂贵且不易变更;运用数码双生平台(PAVE360),车厂可在硬件就绪前12~18个月就探索架构、开发软件并进行系统级验证,加速迭代收敛。

呼应此趋势,ARM的Zena运算子系统(CSS)可透过与PAVE360的虚拟ECU、系统模型与情境模拟整合,协助将车用SoC开发到上车的周期压缩至24~28个月。

从原型 bring-up、设计分割与除错,到系统一致性验证与前期建模分析,Siemens EDA以 Veloce搭配Innexis的硬件辅助方案实现验证左移,串起矽前到系统层级的端对端流程,加速SoC、软件与系统开发验证。若想进一步了解Veloce与Innexis如何支持硬件加速验证与系统级验证策略,欢迎造访官方网站。