发挥最大电池驱动效能的移动多媒体装置系统设计

移动多媒体装置持续推陈出新,不管是PMP移动多媒体播放器、平板电脑,甚至更多元化的媒体应用装置,都朝向功能不断整合的方向发展,在功能方面追加了无线通讯、网络支持,性能方面持续强化核心处理器的运行效能,但这些改变趋势压缩了装置的电源使用效率,改善系统的电源使用效能除了加大电池容量之外,还有哪些选择?

移动多媒体装置持续朝小型化发展,这造成内部PCB的可用空间持续压缩,在相对严苛的设计条件下,系统开发者若仅采取以参考设计为基础进行功能开发,可能在节电、效能、体积等多方面都会影响到终端装置的性能表现。

尤其,Apple推出iPad与iPad 2之后,大力推销其产品具备超过10小时连续使用的电池性能,让一般消费者对于移动设备的电池效能要求变得更为严苛,从以往的连续使用3~4小时,一举提升到至少要连续可用8~10小时之谱。电池效能要求持续增加,系统端的设计也不能一昧地朝加大电池容量方向进行设计,反而必须在更多设计层面强化电池的电源管理,以达到延续产品电池使用效能的设计目的。

针对能源耗用关键元件 选用相对节能、高效能解决方案

观察移动多媒体装置,耗用较多系统能源的元件,应为屏幕驱动、屏幕背光驱动、核心处理器、存储器存取、无线网络存取、电源控制电路...等元件,尤其是屏幕、屏幕背光、核心处理器应是占系统能源较多者,在考量如何提升电池供电效能的设计方针时,必须先解决屏幕、屏幕背光与核心处理器的关键元件选择。

在屏幕方面,目前有多样化的选择,像是LCD、AMOLED、IPS LCD等,针对分辨率与反应速度的不同,又有元件方面的功耗差异,但除了AMOLED目前不需要背光设计外,采取LCD基础的IPS与基本型LCD均需要背光设计。

目前显示屏幕持续朝高分辨率方向发展,以热门的iPhone 4为例,其Retine显示屏幕可在3.5寸面积具备960 x 640的显示分辨率(326ppi),在多数应用设计中,显示屏幕还须整合多点触控设计,在种种的功能追加与性能追加方面,让显示面板的驱动功耗不能只观察显示所需的功耗需求。在节能的设计考量上,显示屏幕基本的运作功耗,讨论相对较成熟的LCD或IPS LCD显示屏幕,在功耗的降低方面可能相对较无空间,在元件部分已经决定了整体使用的功耗基础,但在触控功能的部分,则可选用相对较低的解决方案,或是在小屏幕的应用方案中,不需导入多点触控设计,借此压低整个屏幕模块的驱动功耗需求。

除元件方面的省电性能考量,其实在系统端的驱动控制设计,也可朝向更细致的面板控制设计进行相关功能开发,例如,产品系统若类似数码镜头、移动电话等产品时,可在装置上设置近接感应器,以镜头应用为例,当使用者取镜头透过观景窗进行拍摄、构图时,由于脸部凑向镜头机身,此时LCD的显示内容已无必要性,若系统整合时考量透过近接感应器去关闭LCD显示功能,即可在不同应用模式下减少不必要的功耗发生。此状况也可用于移动电话设计,整合近接感应器在接听电话时关闭屏幕显示,亦可达到相同的节能效果。

同样的,在显示屏幕的背光设计中,目前几乎8成的移动设备都改用更省电的LED背光光源,但LED的省电效能有限,必须透过更多设计方法去进行改善,例如,若是中、小屏幕设计装置,背光的设计就可改成上/下或是左/右侧光型背光,减少LED光源元件的数量,达到减少功耗的设计目的。除此之外,先前针对LCD驱动搭配的近接感应器,也可与LED背光光源驱动控制进行整合,让近接状态时可以适时关闭LED背光光源,这可让使用者的操作体验更好,同时又可达到省电目的。

另外,在背光源的功耗节约设计方面,系统设计者亦可善用光感应器来搭配节能设计,例如,在移动设备的面板正面边缘设置光感应器,借此测得用户使用环境的照明水准,若是亮度较高(强光下或户外),即强化背光驱动功率去改善显示效果,若处于一般室内或是低光源环境,也可同步调低屏幕背光,达到节约整体装置功耗的目的。

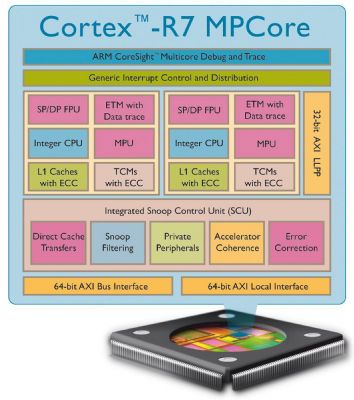

目前多数移动设备,如智能移动电话、平板电脑...等,几乎全面采用相对省电的ARM处理器,而目前ARM系列核心处理器运作时脉也有1G~1.2GHz解决方案推出,但实际上提升核心处理器的效能并非只有持续拉高时脉才办得到,因为单一核心元件若时脉持续增加,元件本身功耗可能相对增加,但效能却无法有效提升,甚至还会增加处理元件散热的额外成本。

以现有的解决方案观察,核心处理器也与桌上型电脑的处理器趋势一样,采取以单颗元件、多个核心的设计方式,去改善单处理器的效能瓶颈,例如,Apple的iPad 2新产品就采取新版A5处理器,利用A5单一封装装载2组ARM核心的设计方式,达到效能较前代产品倍增、多媒体呈现较前代效能有9倍提升的效益。而在采取单元件、多核新设计前提下,其实整体增加的功耗并不多,反而还可以得到效能提升的助益。

无线RF相关模块的省电设计方针

综观移动设备的应用方式,除了处理核心运算应用的微处理器为耗能角色外,若不考量显示屏幕的尺寸所需驱动面板与背光耗能,其实最大的耗能来源应该属于无线、RF射频传输造成的能源消耗。

以目前使用的主流技术为例,无线应用的部分有移动通讯(CDMA、3G/3.5G/WiMAX)、近距离无线通讯(蓝牙、Wi-Fi)为主,以移动通讯应用来说,因为相关数据必须透过长距离的基站交互传输数据,在无线模块的功耗较难进一步压缩,但以免许可的2.4GHz频段的Wi-Fi、Bluetooth更应善用其节能的设计功能,而这也是目前在移动设备使用量最高的中、近端网络应用,对于装置的电池耗用占一定的程度比例,系统设计若未能将其深入考量,可能会影响整体的电源使用效率。

例如,以蓝牙无线传输(bluetooth)4.0技术为例,在一般应用中,蓝牙的规格可支持装置10m周边内的低速传输应用需求,主要是着眼于蓝牙的传输技术,在于低成本、短距离、可互通作业特性,蓝牙无线传输技术一开始在规格制定与功能开发,就以极低功耗(ULP)为开发目的,因为蓝牙主要用来取代如USB或低速周边的传输无线化的目的设计,若无ULP应用思维,可能就成为系统电源耗用的元凶。

而蓝牙无线应用设计,实际上应在因应不同装置连线要求上,进行更精细的设计。例如,当蓝牙用于无线耳机连接应用时,实务的应用可在维持基本连线(无通话)状态时,采取可变连接时间间隔方式,去取得装置持续连接的回应状态;若当蓝牙耳机处于通话状态时,则转换为较高传输率的应用模式,维持最佳无线通话品质。

这种应用模式也可用于如鼠标或其余无线周边,在大量应用时透过BLE(Bluetooth Low Energy stack)技术快速连接,平时装置处于连接但未使用时,仅以链路端点告知双方正在连接范围,随时可以提供连接服务状态,而实际维持装置连接状态确认传送的设备数据,应尽可能减少数据量,同时减少发送次数,以达到节省通讯消耗的功耗为目的。

有效降低待机所需电源 朝极低待机功耗目标努力

若以移动设备的使用惯性观察,一般装置全时工作时间会有2/3或更多是处于待机状态,但在现行装置要求的立即开启、立即使用的应用模式中,让装置系统必须因应此需求,为装置的核心芯片或暂存系统、暂存器、芯片目前待机组态等信息提供最小的维持电力,以在下次开启时让系统快速恢复装置关闭前的操作状态。

一般的思考方式是认为,待机所使用的能源消耗极小,但实际上待机的电源耗用却并非如此!因为多数的电子系统设计,在待机或无负载的状态下,其维持待机的电源消耗仍相当惊人,甚至部分低劣设计的山寨产品,根本就不在乎待机设计,所谓的「待机」模式仅是将LCD屏幕背光关闭,却让核心处理器、系统电路维持在原有全速运行的使用状态,造成开机与待机的电源功耗相当,大幅缩短移动设备的能源使用效率。

尤其是采行电池供电的产品设计,对于待机的要求应该在设计层面投入更多开发资源,例如,必须在产品开发初期即确认装置的不同使用状态对电源耗用的量表,例如,在正常、高速、低速、待机、睡眠、深层睡眠等状态模式下,设定明确的系统功耗指标,让电源电路、主控电路、逻辑电路、周边界面等设计区块,都能尽力呼应到整体的电源管理设计目标,让整体电子电路设计均能依循降低功耗的设计方针进行系统开发。

目前多数的电子装置,例如目前最热门的Android平板电脑,开发厂商大多习惯采用系统芯片业者提供的参考设计再进行相关电路布线改善,较用心的开发者会思考强化节能的附加功能或设计,稍不用心的设计者沿用既有布线设计,而忽略整体的能耗控制设计,造成产品良莠不齐。

在待机模式的能耗降低设计中,若要保有最佳系统反应时间,必须在着手设计前先确认系统关键芯片的待机前数据保存需求,归纳出必须实时保存与将数据取回的转换时间,并针对核心芯片确认其待机条件是否能满足设计,而待机的能耗问题通常在核心处理器问题较少,因为核心处理器通常都会有多种标准运行模式设计,待机模式也会分几种程度性的差异,系统开发时需要重新开发或是调整的空间较少。

反而是周边的功能模块、汇流排、系统芯片的待机方式,多为系统开发工程师来定义,若没有明确定义并进行相关设计要求,就可能出现有时自待机恢复时,却出现显示错乱、触控不灵光,甚至数据回存失误等问题。

一般无硬盘的移动设备,要自待机模式中唤醒,多数必须要求在1,000ms以下,若超过数秒才能唤醒系统,则已失去产品的实用性,尤其在平板电脑、智能手机这类装置中,特别是手机部分,更需要缩短待机唤醒时间,至少要求在500ms内恢复显示与可供用户进行操作的状态,至于如何达到缩短待机唤醒时间的要求,就必须在省电与提高反应速度之间进行权衡设计。

电源电路面临可用空间持续缩小的因应设计

在电子设备的体积持续缩小的趋势下,今日的电源系统开发工程师面对产品不断缩小、应用功能持续增加的挑战,这一方面也意味着电源电路可以分到的PCB主板空间越来越小,此方面的问题将会产生系统的功耗、热处理问题与整体线路布局的影响。

电源工程师在应对这类设计问题,大多只能透过元件方面的技术升级,进行电源电路缩小与效能提升设计,像是常用的电源IC为采MOSFET技术,搭配新式封装设计,但新的应用需求却必须采取更小的空间去乘载这些关键元件,而不只是单单主板面积需要减小,连元件本身的高度,也必须大幅压缩,才能因应新的产品设计要求。

现在的电源IC设计封装,已从SO-8标准接脚封装的设计模式,逐渐进行调整,目前多数设计会采取底侧引脚或底侧焊盘的功率封装设计,而针对高电流应用部分,在一般性的设计方案中多采取PowerPAK的SO-8以5mm x 6mm方式封装,在低电流的主板设计应用方面,新的设计方式为采取PowerPAK 1212-8封装(3mm x 3mm),这类封装的RDS(on)表现佳,尤其在移动设备(如笔记本电脑)采10~15A的DC-DC应用类型,PowerPAK 1212-8封装是相当常见的解决方案。

虽然多数的应用设计中,3mm x 3mm的PowerPAK 1212-8封装似乎已经可以因应多样的设计需求,尤其是产品体积缩小化的开发需求,但实际上还有进一步缩小空间需求的可能性。在DC-DC电路应用中,若要采取更小的设计空间,多数可用双元件封装来替代分离式设计的MOSFET元件,尤其是因应小于5A的负载设计方面,采取Dual SO-8 MOSFET因应小电力的DC-DC绰绰有余,也可缩小元件的占位面积,尤其是当主板的DC-DC应用多为5V、3.3V时,此种元件选用与设计方式更具优势。

而双片式的设计,尤其是在MOSSFET元件方面,选用双片功率封装具有许多好处,因为这类封装方式可以达到较佳的热性能,与取得最大的元件输出电流,原本双芯片的占位空间与元件间的布线都相对造成空间占用,但采双芯片功率封装可以让元件具双芯片优势,同时仅需单芯片的占位空间,等于是简化更多设计同时缩小产品体积,轻松改善元件的占位状态。

电源设计工程师除可善用不同封装特性的电源处理IC,也可在不损及电源安全与维持最佳化电源使用效率的要求下,将DC-DC转换电路的设计尽可能简化、缩小,节省PCB主板空间,甚至可搭载更多主动或被动省电机制,让整体移动设备的电源应用达到最佳化的境界。

- 观察iPad 2缩小体积、维持产品用电时效的设计关键

- 发挥最大电池驱动效能的移动多媒体装置系统设计

- 奥地利微电子推出具有唤醒及省电功能的全新10位元磁旋转编码器

- 英飞凌推动高效率电源转换设计 中电压MOSFET让CanPAK产品系列更臻完备

- 安茂微发表AME5280 DC-DC高效能电源管理控制器

- 持续为终端产品提供高效率及低功耗解决方案 安茂微电子期望成为高附加价值之电源管理IC领导者

- IR收购CHiL Semiconductor 加速开拓高速增长的数码功率市场

- 漫谈节能LCD电视的LED背光区域调光

- Cirrus Logic推出效能及价格均优于类比PFC的数码功率因素校正IC-CS1500及CS1600

- 恩智浦半导体推出业界首款10Gbps CMOS多工器/分工器开关 CBTL02043支持高带宽系统 同时达成最低功耗

- 恩智浦半导体以全球最低待机功耗技术引领潮流 高效GreenChip系列低功耗配接器可同时节省成本与能耗