AMP、Grid-on-Chip、SMP等多核心设计

- DIGITIMES企划

嵌入式产品设计,最大的优势就是可采行最精简的硬件系统来完成指定的功能需求项目,达到操作最简洁、同时兼具低成本与高效能的应用基础,而当嵌入式产品设计被赋予的功能越来越多后,现有的SoC解决方案也开始朝多核心设计架构发展,在原有设计方案下,提供更高的处理效能与系统反应效率...

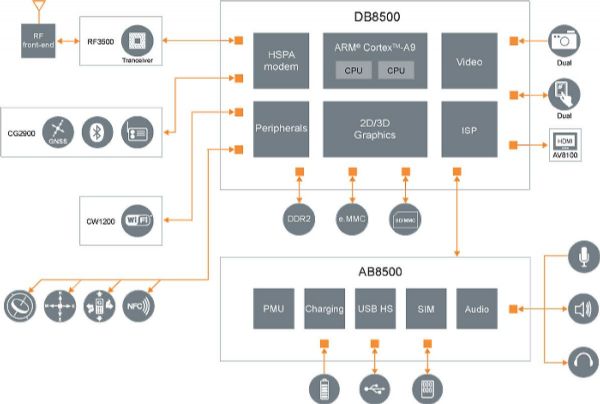

利用SoC(System On Chip)的手段,把多处理器甚至是以往采离散式设计型态的图形处理、音效芯片、DSP(Digital signal processing)、视讯编?解码器等,一一整合成一个单片型态的处理核心,利用这种开发手段,SoC不只较同等的单核心设计方案更为精省,且多核方案可以有效将运算负荷透过各专用核心纾解运算可能产生的瓶颈,同时主运算核心也不用一昧地利用拉高系统外频来增加效能,而是可用SMP对称核心的分工运算,达到相同或少许提升时脉下即可获得倍增的运算效能。

以单一SoC设计或是局部SoC来进行功能整合,是嵌入式应用领域相当常见的设计方案选项,利用整合芯片的高度芯片内连接与整合,可让原先具固定占位面积的料件可以因为芯片内的功能核心整合,让数个芯片微缩至仅需一个芯片就能完成,一方面减少零组件数量,同时也能降低系统的料件成本与强化系统的功耗表现。

但要让采多核设计方案的硬件架构充分发挥效能,除硬件在芯片、电路载板布局各方面进行工程段的开发努力外,基本上仍须加入软件团队,针对多核架构的硬件现况,来将系统软件做最有效的多核性能调校整合,仅有系统与硬件的多核最佳化搭配,才能让嵌入式系统可以在低功耗、高度简洁的架构设计下,维持近似或更低的耗能,同时可处理的数据量、系统反应效能却能因为多核架构而同步提升。

多核心整合架构 应强调单一核心最佳化运行

虽然现有嵌入式SoC趋势是往多核心方向发展,但实际上在进行应用核心的多核设计之前,仍必须针对多核心设计进行应用划分设计准备,尤其是要针对重要架构的细节进行深入检查。

例如,网络路由器的嵌入式设计方案,在Level-2 router或Level-3 router产品,多数的产品设计方案都若朝为传统路由器架构更多管理功能、或应用方案,让原产品可以扩充如Level-4以上的路由器应用方案,来达到产品差异化设计的目标。若是单核心设计方案,为提升追加功能性的执行效能,通常只能利用提高外部时脉进行性能提升,但单核心方案在性能提升方面可能会因物理限制而无法无限制的提高,势必要寻求多核设计方案来改善产品表现。

现有的多核心元件,工作外频可以在800MHz~2GHz不等,核心的数量可以从多核心的最低量双核一直到8~16核心不等,但想利用多核设计来强化整体运算效能,仍必须考量系统底层的支持特性,在一般设计中单核心方案强化效能可从增加快取或是提升外频来冲高效能表现,而多核设计方案除了利用多核心的硬件优势外,如何让多核心各个单一核心可以在最佳化的状态运行,就考验着分配运算任务的处理效率。

多核心设计方案 并非核心数越多效能就能翻倍

AMP(Asymmetric multiprocessing)或称为ASMP的设计方案,会把运算任务分成两大部分,一部分是控制相关任务,而另一部分为数据相关任务。像是数据相关的任务如使用DSP来进行,而利用一组通用CPU来进行系统的正常运行,这种设计方案可让系统与除错工具都相对单纯。

在嵌入式设计方案反而较常应用对称式(Symmetric Multiprocessing;SMP)多核心设计方案来实现,即使SMP的运算管理相对较AMP单纯许多,但实际上不管是AMP还是SMP设计方案,当核心数量超过2个以上后,运算性能的提高效益就不可能呈核心倍数增长,因为宝贵的CPU运算周期会部分用于多核心处理器的运算任务协调,致使整体的SoC运算效率提高的效益受到限制。而因多核硬件整合所提升的效能,并非核心越多、效能就能得到对应的倍数提升,反而必须视如何维持高效率的工作分派运算与协同处理,才能得到接近的提升效益。

Grid-on-Chip多核设计方案

Grid-on-Chip即芯片上栅格(或简称「栅格」)模式,为由许多完整独立之与网络互连的运算节点所组成的多处理器系统。在Grid-on-Chip中每个芯片共享相邻实体链路,但每个运算单元仍维持独立的网络处理节点。

Grid-on-Chip也可以说是分散式多处理系统,可以算是AMP、ASMP的设计方案之一。应用Grid-on-Chip首先要分割系统、寻找合适的节点进行通讯,即便是高端的Grid-on-Chip系统可在执行过程自行重新配置资源,但开发时仍须针对Grid-on-Chip思考系统功能与每个运算节点的系统分配问题。

除分割问题外,Grid-on-Chip系统其实在设计限制算是最少的,即便系统遭功能分割,每组运算节点的设计基础仍等同独立的子系统运行,Grid-on-Chip模式系统与其他设计的优点是,Grid-on-Chip可以很容易地与软件进行整合,系统也能在单一栅格范围内完成应有的计算任务,此外,Grid-on-Chip系统设计方案在除错工作亦相对简单不少。

至于「分割」,是Grid-on-Chip的主要优势,但实际上也是分割的系统让Grid-on-Chip的缺点特别凸显,因为系统的分割让架构难以再分配资源,尤其Grid-on-Chip在面对不可预期的计算要求时,系统的灵活性就会较低。

SMP的多核心设计方案

至于目前最普遍的设计方案,就属对称多处理器架构(SMP)莫属,此为single-image操作系统执行在2或数个共享处理核心、存储空间的设计方案,而这些核心处理器在各自的核心架构上大多为一致设计,在SMP模式架构下,系统可在如同一个处理器核心的基础上进移动态分配运算工作。

尤其在可快速重新分派处理任务的能力方面,是SMP系统架构的优势,这也是SMP系统较AMP/ASMP或是Grid-on-Chip等多核心方案中最具使用灵活性与系统适应性的设计方案,运行于SMP的实时操作系统的架构灵活度,可在不牺牲性能的条件进行任务分派与实时回应系统需求。

每个SMP架构都必须具备两个要件,一是对称之共享存储器的多核心处理平台,另一个是必须支持SMP架构设计的操作系统,现今不只是Android嵌入式系统,多数嵌入式应用平台已支持了SMP架构应用,同时操作系统的选择也较以往多元,开发人员可以快速导入较熟悉的系统平台,在最有效率的时程完成SMP嵌入式应用开发,不管是移植旧有的应用设计方案,或是重新架构新的硬件架构,SMP架构方案可轻松、快速地运用多核心硬件优势来提升整体运行效能。

但整合SMP应用时仍须注意一些问题,例如,若嵌入式设计需要考量实时反应需求,搭配支持SMP的实时操作系统(Real-Time Operating Systems;RTOS)虽然不会影响实时反应效能,但使用SMP即会因为系统整合,导致系统缺少更高端与可变中断的反应时间,这在惯用单处理器的RTOS系统产品上可能会与采多核心设计的产品表现略有差异。

此外,SMP应用于嵌入式系统的另一个问题,在于系统资源的竞争设计,虽然SMP的优点是硬件资源共享设计,这同时会让嵌入式SMP系统具系统灵活度与更高的适应性,但这个优点同时也是个缺点!因为资源共享的关系,也让SMP的系统资源竞争会出现较难因应且无法预期的性能变化,开发人员在架构应用时需同时考量应用的设计架构。

- 高分辨率发烧 移动设备多核GPU应用成趋势

- AMP、Grid-on-Chip、SMP等多核心设计

- Smart TV、STB带动嵌入式处理器朝多核心架构重点升级

- Sophia System推出ARM 4G ETM高速追踪除错器

- ARM与台积公司携手共创64位元处理器最佳化

- iPPea TV支持Android系统数码电视外接器

- Intel Xeon E5系列 获Top500超级电脑爱用

- 向日葵5.0携手高通创锐讯布局远程控制一体化

- Intel Core处理器提供更惊艳的移动运算体验

- Silicon Labs新无线IC简化嵌入式设计与效能

- Android NDK应用程序将可支持MIPS架构

- 2012高通Uplinq大会演示移动技术平台生态