从降低电压、智能动态调整改善芯片功耗问题

- DIGITIMES企画

芯片功耗问题,已成为现代移动设备、3C产品最重要课题,因为芯片功耗若无法控制在一定程度,终端产品为了延长电池工作时数,势必需要追加电池容量,甚至过高的芯片功耗也会造成设计方案还须追加主动散热设计,如此环环相扣造成产品在体积、耗能、效能各方面都趋于劣势,降低了终端产品的市场竞争优势...

一般进行IC芯片设计时,大多会先以功能性考量为主,但若要因应市场竞争,除了功能要求外,芯片本身的功耗表现,已经成为解决方案在市场竞争的重要指标,因为芯片的功耗表现不只影响整体配套设计的复杂度,甚至也会成为左右终端产品的市场竞争力指标。

以移动终端产品为例,若采行的芯片解决方案在功耗表现方面设计不佳,就会造成电池的效能低下,导致产品电池续航能力出现明显劣势!而设计方案中若为了提高整体效能,高功耗也会连带使设计方案的散热需求变得更高,不只机壳需要考量设置更多散热孔位,甚至还需在设计方案追加主动散热机制,例如更大的散热片或是散热风扇,自然造成终端设计产品的尺寸不易微缩,或是使产品出现高热的设计劣势。

善用低功耗元件与新材料 打造省电移动设备

如果在设计方案中导入低功耗芯片元件,可在有限电池容量下达成设计方案要求的电池效能设定,芯片的运作温度也不会飙升太多,自然就能减少散热片元件成本,让BOM料件成本得到最直接的精省,令产品的成本结构更具竞争力。

降低芯片的功耗,还可以从改用更低耗能的材料、增加智能耗能调节、降低芯片工作电压等多种方案,来降低芯片设计方案的功耗。

通常,使用新的低功耗材料,是降低芯片功耗的最快捷径,但新材料的设计门槛相当高,一方面不光是电学的问题,而是将设计层次拉高到材料科学的问题,通常这对一般无晶圆厂的设计公司是较难掌控的部份,投入成本相对较高,但对功耗改善表现却是相当显着。

即便改善材料是最有效降低功耗问题的方案,但面对高成本的实验与材料技术奥援,在一般元件设计方面并不容易达成, 尤其是采行高效电子迁移的材料,可直接降低芯片本身的功耗问题。例如,若在标准化的CMOS产品加入磁性材料纳米材料,或是新颖的石墨烯改善料件本身的特性,也是相当常见的功耗改善作法。若在此功耗改善方案中,业者必须具前端的材料科学技术能力,同时也必须有丰沛的元件制造经验,才能掌握透过材料改善元件的功耗问题的技术能力。

像是CMOS产品中的低功耗设计,常会以InGaAs(砷化铟镓)材料,来进行功耗表现改善,像是Intel在CMOS设计中就尝试以此设计方向,来降低芯片的工作电压,透过驱动电压的调降,进一步改善整体芯片的功耗表现。另一方面,使用石墨烯或在芯片材料添加纳米技术材料的方式,也是未来超低功耗元件的重点设计方案,目前TI已着手进行相关设计开发工作,期待在新设计中创造超低功耗芯片的应用基础,透过降低材料的电阻值,让整体芯片的功耗问题可以获得大幅改善。

透过智能耗能调节达成节能要求

除了材料外,改善能耗更务实的作法,则是在芯片设计时即考量节能机制,例如透过不同层次的睡眠设计,让芯片的耗能单位设计,可以在不同深浅程度的睡眠模式获得弹性调整的空间,达到进阶节能的目的。

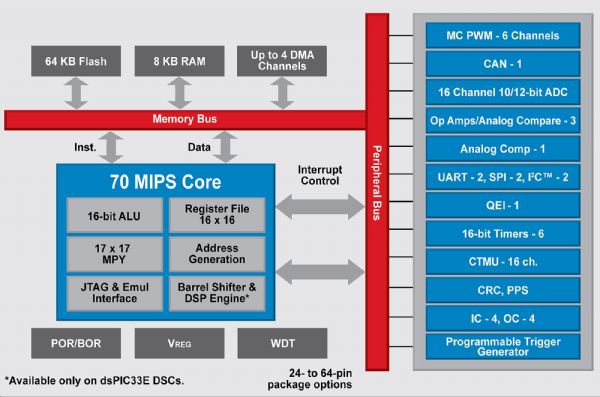

一般的设计方案中,通常驱动电压越低、驱动的时脉越低,也会让整体芯片的功耗获得压低的成效,但付出的代价可能就是牺牲运作效能!这种透过局部功能性的关闭、或是芯片整体因应不同睡眠机制的功耗控制设计,在简单的芯片设计中效果较不显着,反而是在高度整合的SoC(系统单芯片)、CPU与MCU元件上,透过区域节能与电压、时脉动态调校设计达到的节能效益,可以达到较高的节能效益。

像是Intel在最新的中央处理器中,就设置了Turbo模式,即在正常模式下维持标准运行状态,避免系统持续维持在高时脉的条件下运作,但当用户需要高效能的处理数据需求时,即可透过系统热键启动中央处理器的Turbo功能,此时驱动电压、时脉可适时提高,让芯片获得更高的驱动电压,提升频率榨出更多处理效能,也就是利用电池效能去交换处理器效能的折衷设计方案。

节能机制的另一种实践方案,就是采用SoC设计架构。SoC本身是将多种功能目的芯片整合为一的单芯片产品,结构为内部连结多芯片的单一封装设计,如果在设计这类SoC芯片时,即将电源管理的需求一并考量,即可在各个功能芯片连接设计中,追加如控制单元芯片开关的dark silicon设计概念,在未使用该项功能芯片时透过省电控制机制令该单元不驱动、不运行,即可达到更具效率的省电效用。此设计方案在移动运算应用的整合处理器设计方案中尤其常见,像是多核心设计的嵌入式SoC,即能因应移动设备的运行状态,动态控制驱动核心数量与重点功能的开启与关闭,达到进阶节能的设计目的。

利用降低驱动电压达到芯片更直接的节能功效

前述透过材料的调整,虽然也能达到降低驱动电压的效用,但此处谈到的降低电压,反而是因为采行更微缩的线路制程,因为芯片内晶体的连接距离变得更微缩、芯片距离更短,因此芯片可使用更低驱动电压达到相同的导通或运行效果,像是工作电压自1.5V上下的芯片,经过新一代的制程设计后,驱动电压即可降至1.35V亦能稳定运作,光是节省的0.15V水准,就能替原芯片达到60%以上的节能功效。

但透过制程微缩改善功耗的手法,近年也逐渐出现技术瓶颈,因为持续微缩的制程技术,目前已达接近极致的状态,目前最新方案需要以3D制程或是更先进的微缩设计概念,才能获得更进阶的功耗改善效益。

而利用3D制程的概念,主要源自缩短内部晶体传输距离的概念,将内部Inter connect的距离进一步缩短,此即可减少IC内部传输功耗,进而降低IC本身的功耗。一般来说,缩短连线距离的方案是追加芯片内的金属层,而在芯片内的互连层设计中,新方案是利用3D矽晶穿孔(TSV)技术进行设计,但实际上TSV设计方案在制程耗费的成本相当高,省电功效对应芯片制作成本的效益换算,却未必划算。