8、16或32位元MCU的方案选择关键

- DIGITIMES企画

微控制器对于开发人员来说,可以说是再熟悉不过的关键元件,微控制器可解决设备的控制需求,甚至可开发更多元的整合应用,具体实践令设备具智能化的应用设计,而在不断更新的集成电路整合技术加持下,微控制器也从最普遍的8位元进展至16甚至32位元,单核心的设计也出现了多核心的版本,甚至还有GHz等级的运行时脉...

微控制器零组件,可以说是嵌入式产品设计必备的开发重点,若仔细思考与观察,会发现近年来的微控制器正面临跳跃性的时代发展,尤其是强调智能应用的移动设备的大量采用与整合下,在市场的趋力持续推进微控制器的发展进程,使MCU的技术进展足以发展出达到与常规电脑运算用处理器相匹敌的技术架构。

产品持续微缩 MCU功能复杂度越来越高

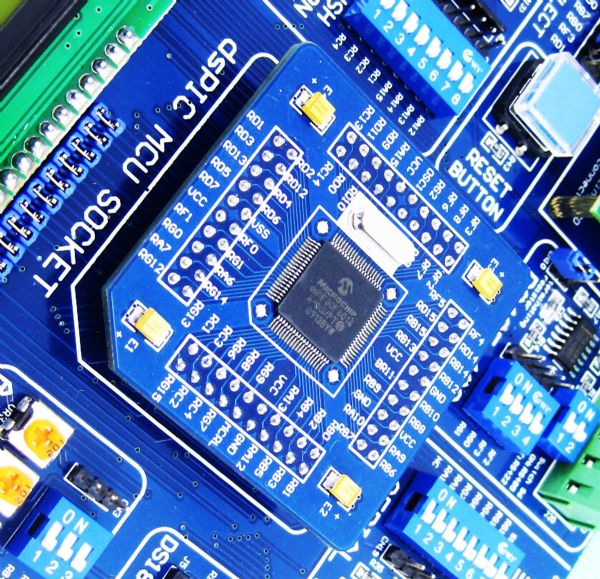

尤其是在近来电子产品持续要求体积尺寸缩小化,同时也造成PCB的使用层数、设计密度越来越高,对于以往采大量离散元件构筑的产品设计,现在新的设计都必须多采行现成的整合方案,来因应机壳内可用的设计空间持续压缩的限制,尤其是以前大量使用离散元件方案来架构产品功能,在载板空间相对受限的产品上,就必须采行高度整合、大量整合的应用方案。

尤其是新一代的平板电脑、智能电话,产品尺寸大幅缩小、极致薄化,这已威胁非整合元件的市场竞争力,反之,若设计方案已同时有大量离散元件设计方案、与运用矽整合技术大量离散元件整合在同一封装中,不仅一次解决了载板面积有限的问题,在大量整合的设计也让设计的应用方案更加多元。

MCU的设计资源越来越丰沛 加速开发周期

MCU在元件方面,大多低端的控制用途,多数仍会采行8位元产品来进行设计方案,但实际上新型态的应用设计已经开始朝向采16位元甚至32位元的MCU,来进行嵌入式应用的关键整合核心元件,例如以ARM的MCU产品来说,ARM Cottex的处理器,在近几年的用途越来越多样化,不再仅限单纯的自动化控制设计用途。

甚至是早期ARM的整合方案,都必须考验开发团队自行研发应用软件的能力;但现今基于ARM的软件工具、参考设计等开发资源越来越丰沛,尤其是开发的SDK完整度极高,不仅加速了产品整合方案的可实行性,也让开发周期大幅缩短,加速产品从构思到研发、上市的耗费时间,也让研发者与开发方案,更能面对产品未来的升级与扩充设计。

8位元MCU常见的设计限制与效能瓶颈

检视8位元的MCU,其指令长度为8位元指令,而32位元MCU,指令长度采32位元,事实上,即便是8位元的MCU,实际上多项指令早已是16位元甚至24位元长度。部分产品研发人员或许会认为,MCU应该维持精简,使用8位元设计已足以因应多种设计需求,但实际上若是深入了解C的编译环境,若开发产品会以C来进行产品架构,实际设计时所使用到的函式库,所处理的大量信息都会以16位元为多,若只使用8位元MCU来处理这些数据,将会造成MCU必须耗上2~3倍的时钟周期来处理这些运算元,造成运算效能低落。

当然,这种运算反应低落的状态,若是因应简单的自动控制,可能会因为产品设计架构本身就相当简单,让这种不效率的状况不容易体现在产品设计的最终成果,在面对小型专案的设计需求上使用8位元或16甚至32位元的MCU并不会出现显着差距,反而是元件选择的成本问题,是更须重视的项目。

但若是发展控制项目更复杂的设计方案,时间周期运算的不效率问题,就很容易被放大,甚至造成设计方案出现运行反应迟缓的关键限制。同样的问题也会发生在当设计方案的存储器控制需求方面,例如,当设计方案需使用更大容量的内置储存元件时,8位元的存储器定址能力,势必会比16位元定址能力更有限。尤其是8位元的MCU在处理整数运算时,因原指令的限制问题,会让单纯的运算产生大量的内存存储器提取与暂存动作处理,影响了微处理器的运行效能。

评估MCU效能 从执行效率、功耗、元件特性整体考量

此外,也不是说更高位元的MCU就是最佳方案,一般考量使用MCU的等级,并不是光以效能与处理能力为唯一考量,而必须同时分析设计方案的功耗要求、嵌入式设计方案的性能要求,去做最佳化的应用方案选择。

例如,当面对运算复杂度不高、对电池寿命要求较高的设计方案时,我们会寻求具高省电能力的精简MCU方案来进行设计,在效能要求较电池寿命更高的应用型态时,设计方案就应当选择较高性能(如16位元、32位元MCU),甚至元件的外部时脉更快的方案,来架构产品。对于MCU的性能指标来说,一般我们会以Dhrystone基准来进行评估,以DMIPS/MHz 的Dhrystone性能表现,来进行MCU的性能差异比较。

在功耗优化设计方面,基本上MCU本身视架构不同,大多有其降低功耗的设计方案,让其在元件端就能达到一定程度的低功耗要求,以目前最常见的ARM MCU解决方案为例,在ARM MCU的内部结构,已内建降低功耗设计方案,例如在Cortex-Mx系列MCU产品,大多已在核心架构中支持睡眠模式,同时也能在应用工作处理完成后,处理器随即返回睡眠模式等待下一次工作触发的极低功耗设计型态,来架构终端应用产品。

甚至是如前述讨论的8位元MCU可能存在的问题,在于开发的专案程序码,因为MCU本身的指令限制,让单纯的运算需要2至3个运算周期才能完成,若同样的运算可能在16或32位元MCU方案中,只需要1个运算周期就能完成,两者的差异是前者需面对大量的数据提取与暂存才能完成运算,后者是只要1次就完成直接产生结果,而数据的提取或暂存,若涉及外部I/O与快闪存储器的读/写,完成整个运算需要消耗的功耗,可能会出现比16或32位元MCU方案更多的状况。